# Validation and verification

#### of real-time data processing system in programmable devices for Digital J-PET scanner DAQ system

3rd Symposium on Positron Emission Tomography

Cracow, 2018

### Validation and verification

"Validation. The **assurance** that a product, service, or system meets the **needs** of the customer and other identified stakeholders..."

"Verification. The **evaluation** of whether or not a product, service, or system **complies with a regulation, requirement, specification, or imposed condition**..."

### Validation of developed system

• Key functionality assumptions based on previous project iterations

- o continuous triggered readout

- modularity and parametrization of subsystems

- Bottlenecks candidates

- resources

- throughput

- Next steps in further development...

# Verification in reference to programmable devices

• Data source emulation

HLS (High Level Synthesis) simulation environment for implemented modules

• Complementary HDL simulation

Testing and evaluating design on hardware

Statement of

#### Data source emulation

**Digital J-PET scanner module data generator in python.** Why python? Why Jupyter notebook?

- Jupyter: No hardware setup or configuration needed. Work and further development can be easily done online in web browser

- Python is high-level programming language, so creation of utility applications is <u>fast</u> and code is <u>brief and legible</u>.

- Python contains <u>scientific libraries</u>, so we can easily <u>extend and integrate</u> current application with <u>complex mathematical models</u>

### HLS simulation environment for designed modules

**FPGA** subsystems prototyping and testing in Vivado HLS IDE.

- HLS programming language abstraction enables <u>implementation</u> and rough debug on main functionality <u>faster</u> than traditional Hardware Description languages

- HLS enables agile design optimizations with pragmas

- Software algorithms migration to programmable logic with HLS is easier because of same abstraction level implementation (C/C++)

Timing (ns)

Summary

Detail

Instance

Loop

ap\_clk 5.00

Latency (clock cycles)

Summary

Latency Interval

min max min max Type

0 0 0 0 none

Clock Target Estimated Uncertainty

2.62

0.62

| state = IDLE;                           |

|-----------------------------------------|

| }                                       |

| else                                    |

| { state = IDLE; }                       |

| head->errs = 0;                         |

| head->ev_num = 0;                       |

| head->f_id = 0;                         |

| head->wc = 0;                           |

| *busy = 0;<br>*data ready =0;           |

| ducu_ready =0,                          |

| break;                                  |

| case HEADER:                            |

| if(input.den_in -= 1)                   |

| from hand ou nom - linewit data in t. / |

## **Complementary HDL simulation**

#### HDL testbench and transactions simulation

- Examination of low level signals in intergration testing and subsystems simulation

- SystemVerilog based verification for HLS modules testing on low-level abstraction

- AXI transactions as freugent method for in hardware FPGA testing, monitoring, slow-control and debug. Common interface in proposed system design

| lame                  | Value     |          | 102,200 ra | 102, | 400 na   | 102,60  | 0 ns   | 102 |

|-----------------------|-----------|----------|------------|------|----------|---------|--------|-----|

| ap_start              | 1         |          |            |      |          |         |        |     |

| ap_done               | 0         |          |            |      |          |         | uuuu   |     |

| ap_idle               | 0         |          |            |      |          |         |        |     |

| ap_ready              | 0         |          |            |      |          |         | uuuu   |     |

| data_in_address0[9:0] | 3000      | X00K     |            |      |          |         |        |     |

| data_in_q0[31:0]      | 300000000 | 10000000 |            |      |          |         | 000300 | 0p  |

| wr_in_eodw_V(0:0)     | 1         | 0 (      |            |      | 1        |         |        |     |

| wr_in_start_V[0:0]    | х         | х        |            |      | 1        |         |        |     |

| wr_out_loaded_V[0:0]  | 1         | 0        |            |      | 1        |         | 0100   | ixa |

| wr_out_ect_V[0:0]     | 0         |          |            | 0    |          |         | 0 0    | 0   |

| fsf_den_out_V[0:0]    | 0         | 0        |            |      | 1 0      |         | 0      |     |

| fsf_data_out_V[31:0]  | 00000000  | 00000000 |            |      |          | (a) (a) | 2000   | xbc |

| fsf lane up V[0.0]    | 1         | 0        |            |      | <u> </u> |         |        |     |

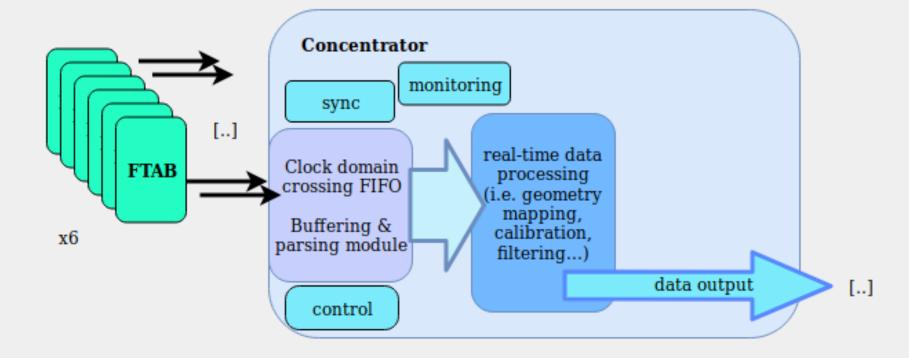

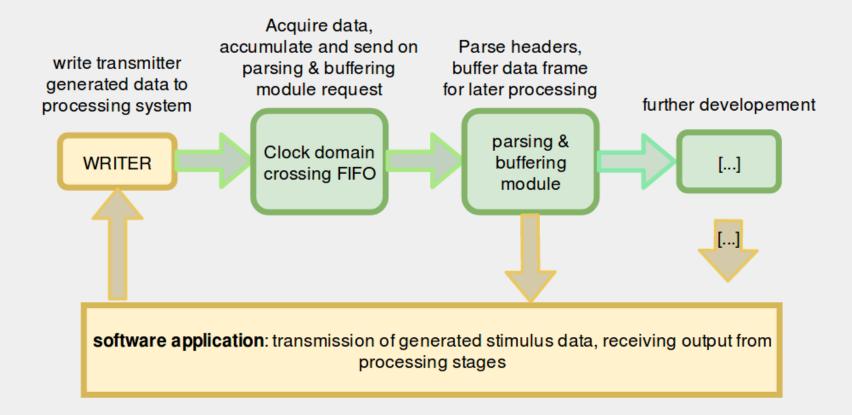

#### Data processing system – conceptual design

### Testing and design evaluation in hardware

#### Summary & conclusions

- Suitable verification enviroment enables faster developement of modules

- Variety use of dedicated tools, software and programming languages is essential in complex HW/SW systems development

- Scripts, applications and designs reuse its a nice to have approach while working on R&D

- Parser and interfacing tests ongoing

- Module-wise coincidence finder as a next step